# Research on a Pulse Generation Method of Dual-Channel Synchronous Reloading\*

WANG Xingui, BAO Wenxia, YANG Zhiyong, WANG Jing, YU Minghui, WU Di\*

(School of Optoelectronic Science and Engineering, Soochow University, Suzhou Jiangsu 215006, China)

Abstract: Transient pulse signal has been widely applied in industry control and optoelectronic communication. A pulse generation method of dual-channel synchronous reloading is proposed. Based on this, a nanosecond transient pulse generating system is developed, which is composed of clock generator, dual-channel synchronous reloading counter and signal edge trigger. Dual-channel synchronous reloading counter counts the stable clock signals with the same phase produced by the clock generator and then outputs indicator signals. The indicator signals can output the pulse signal directly through the signal edge trigger. The experimental results show that this method is able to generate nanosecond pulse signal with adjustable pulse width. The minimum pulse width and adjustment accuracy is 0.833 ns. Compared with other methods, the pulse width is narrower and the adjustment accuracy is higher.

Key words: dual-channel synchronous reloading; transient pulse generator; FPGA

**EEACC: 1210**

doi:10.3969/j.issn.1005-9490.2022.01.009

# 双通道同步复装载脉冲发生方法研究\*

王薪贵,鲍温霞,杨智勇,王靖,禹明慧,吴迪\*(苏州大学光电科学与工程学院,江苏苏州 215006)

摘 要:瞬态脉冲信号在工业控制、光电子通信等领域应用广泛。提出了一种双通道同步复装载脉冲发生方法,并基于此方法设计了一个纳秒级瞬态脉冲发生系统。该系统由时钟发生模块、双通道同步复装载计数模块和信号边沿触发模块组成。时钟发生模块输出相位相同、频率稳定的时钟信号。双通道同步复装载计数模块对生成的时钟信号进行计数并发出指示信号。指示信号通过信号边沿触发模块直接输出脉冲信号。实验结果表明:该方法可以生成脉宽可调的纳秒级脉冲信号。最小脉冲宽度和脉宽调节精度为 0.833 ns,与其他窄脉冲发生方法相比,脉冲宽度更窄,脉宽调节精度更高。

关键词:双通道同步复装载;瞬态脉冲发生器;FPGA

中图分类号:TN782

文献标识码:A

文章编号:1005-9490(2022)01-0051-08

高速脉冲信号作为现代电子技术的基础,在电子通信、工业控制、采集和测量等方面都有广泛的应用<sup>[1-2]</sup>。随着信息科学的不断发展,为了使电子装置具有更加良好的通用性和灵活性,越来越窄的脉冲宽度与高精度的脉冲宽度调制是高速脉冲信号发生的重要发展方向<sup>[3-4]</sup>。

20世纪初,人类就已经开始利用弦振动产生一定频率的脉冲信号。随后,人们又先后使用气体和火花放电等方法将产生的脉冲宽度由毫秒级减小到了微秒级<sup>[5]</sup>。其开发成本高昂,设计过程复杂,已经很少再被使用。

从 20 世纪 70 年代开始,原有的模拟信号处理开始被数字信号处理取代,采用集成式逻辑门电路控制

生成脉冲信号的方法得到了应用<sup>[6]</sup>。随着计算机技术的不断发展,可编程实时脉冲发生电路成为了主流。单片机、微控制器等器件具有成本低廉、体积小的优点,利用时钟信号控制其输入输出口来产生脉冲已经成为目前较为常用的一种方法<sup>[7]</sup>。然而由于这类器件时钟频率一般较低,所以精度相对较低,而且受到外围模拟电路的限制,控制灵活性差、抗干扰能力弱<sup>[8]</sup>。FPGA等可编程逻辑器件以其灵活性高、实时性好、数据处理高效等显著优势在脉冲信号发生领域具有不可比拟的优越性,实现了纳秒级精度的脉冲发生与脉冲宽度的调制<sup>[9]</sup>,满足了绝大多数测量与控制的需求<sup>[10]</sup>,但是进一步减小脉冲宽度需要很高的工作频率,通用FPGA一般难以达到要求。搭建半导体晶体管电路的

方法虽然可以实现极窄脉冲信号[11-12],但受制于电路设计,无法实现脉宽调节,很难加以利用。而基于非线性传输线的边沿压缩技术,通过传输材料、技术工艺和参数的设置,可以大大压缩脉冲信号边沿的过渡时间产生皮秒级的脉冲信号,但是非线性传输线技术并没有公开,具有技术垄断性[13]。除此之外,采用极化门控技术产生分辨率更高的脉冲的技术才刚刚起步,设计十分复杂,生成的脉冲宽度也很难加以控制并利用,是目前的前沿课题[14-15]。

针对目前 FPGA 设计的脉冲信号发生方法存在的问题,本文提出了一种双通道同步复装载脉冲发生方法,并基于此方法设计了一个纳秒级瞬态脉冲发生系统。系统采用双通道结构对频率相近的时钟信号上升沿技术产生指示信号输出,利用两个通道之间产生的游标效应,对指示信号逻辑运算直接生成纳秒级瞬态脉冲,在此基础上,还可以通过更改计数值,实现纳秒级精度的脉冲宽度调制。

# 1 双通道同步复装载脉冲发生方法

目前通用 FPGA 最高工作频率通常在为500 MHz 以下,无法满足直接生成纳秒级瞬态脉冲的发生要求。本文设计了一种双通道同步复装载脉冲发生方法,包括时钟发生(Clock Generator)、同步复装载计数(Reloader\_A、Reloader\_B)和信号边沿触发(Signal edge Trigger)三个部分。时钟发生部分主要生成两个频率相近的时钟信号和一个装载信号。同步复装载计数部分是由两个可以被装载信号同步装载计数值的计数通道共同组成的控制模块,每个通道对各自的时钟信号进行计数并生成指示信号,将生成的两个指示信号通过信号边沿触发,实现输出电平翻转发生纳秒级精度的窄脉冲。

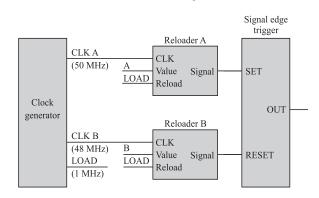

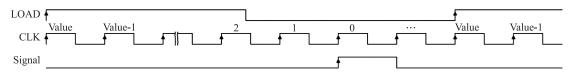

如图 1 所示,双通道同步复装载脉冲发生方法 首先产生两个频率相近的时钟信号 CLK A、CLK B 和一个 1 MHz 的装载信号 LOAD。CLK A 频率较 高,作为同步复装载计数部分的第一通道 Reloader A 的计数时钟, CLK B 频率略低, 作为第二通道 Reloader\_B 的计数时钟。两通道分别对各自的输入时 钟脉冲进行计数,计数值分别为输入的 A Value 和 B\_Value,每当 LOAD 时钟信号的上升沿到来时,A\_ Value 与 B Value 就会再次被同步地装载到两个计 数通道中,重新开始下一轮计数。每次计数值到达 装载的计数值 A\_Value 或 B\_Value 时,对应的计数 通道就会产生一个指示信号 Signal, 通道 Reloader\_A 产生的指示信号为 SET 信号,通道 Reloader\_B 产生 的指示信号为 RESET 信号,由于计数时钟频率不 同,产生的 SET 和 RESET 信号上升沿产生时刻会有 一段相位差,在SET信号上升沿和RESET信号的上 升沿触发输出信号电平翻转,就可以产生一个脉宽 可调的瞬态脉冲信号。LOAD 信号不断地将两个通 道的计数值同步复装载,这个脉冲信号就会以一定 频率不断地出现,实现脉冲发生。双通道同步复装 载脉冲发生时序图如图 2 所示。

图 1 双通道同步复装载脉冲发生方法示意图

图 2 双通道同步复装载脉冲发生时序图

当产生的装载信号 LOAD 上升沿到来时,计数值 A\_Value 与 B\_Value 就会同步被装载到两个通道中。两个通道分别使用 CLK\_A 和 CLK\_B 进行计数,每个时钟信号的上升沿计数值减1,当计数值变为0时,两个通道分别输出 SET 和 RESET 信号,SET 信号的上升沿使输出 OUT 置1,RESET 信号的

上升沿使输出 OUT 置 0,产生瞬态脉冲信号。当 LOAD 信号的下一个上升沿到来时,实现双通道计数值的同步复装载,重复脉冲信号的产生过程。

生成的脉冲信号宽度与输入的计数值 (A\_Value、B\_Value)和输入时钟(CLK A、CLK B)的 频率有关,输入时钟的频率决定脉冲信号宽度的最 小分辨率,以 48 MHz、50 MHz 为例,48 MHz 时钟计数一次需要的时间为 1/48 MHz,50 MHz 时钟计数一次需要的时间为 1/50 MHz,通过上面的分析,两个通道计数完成的时间差就是输出的最小分辨率,最小分辨率可以计算为

$$\frac{1}{48 \text{ M Hz}} - \frac{1}{50 \text{ MHz}} = 0.833 \text{ ns}$$

(1)

即生成的最小脉冲宽度为 0.833 ns。

通过改变计数值生成的脉冲宽度 W 计算公式

如下:

$$W = \begin{cases} \frac{\text{B_Value}}{48 \text{ MHz}} & \frac{\text{A_Value}}{48 \text{ MHz}} \geqslant 0 \\ 1 000 \text{ ns} - \frac{\text{B_Value}}{48 \text{ MHz}} + \frac{\text{A_Value}}{50 \text{ MHz}} & \frac{\text{B_Value}}{48 \text{ MHz}} - \frac{\text{A_Value}}{50 \text{ MHz}} < 0 \end{cases}$$

$$(2)$$

根据脉冲宽度计算公式, A\_Value、B\_Value 取各值时所对应的脉冲宽度如表 1 所示。

表 1 脉冲宽度与 A\_Value、B\_Value 取值的关系

单位:ns

| B Value | A_Value |         |         |         |     |         |         |         |         |  |  |  |

|---------|---------|---------|---------|---------|-----|---------|---------|---------|---------|--|--|--|

| D_value | 0       | 1       | 2       | 3       |     | 46      | 47      | 48      | 49      |  |  |  |

| 0       | 0.000   | 20.833  | 960.000 | 940.000 | ••• | 80.000  | 60.000  | 40.000  | 20.000  |  |  |  |

| 1       | 980.000 | 0.833   | 980.833 | 960.833 | ••• | 100.833 | 80.833  | 60.833  | 40.833  |  |  |  |

| 2       | 41.667  | 21.667  | 1.667   | 981.666 | ••• | 121.667 | 101.667 | 81.667  | 61.667  |  |  |  |

| 3       | 62.500  | 42.500  | 22.500  | 2.500   | ••• | 142.500 | 122.500 | 102.500 | 82.500  |  |  |  |

| •••     |         | •••     | •••     |         | ••• |         |         |         |         |  |  |  |

| 46      | 958.333 | 938.333 | 918.333 | 898.333 | ••• | 38.333  | 18.333  | 998.333 | 978.333 |  |  |  |

| 47      | 979.167 | 959.167 | 939.167 | 919.167 | ••• | 59.167  | 39.167  | 19.167  | 999.167 |  |  |  |

A\_Value 和 B\_Value 取值均为 0 时,脉冲宽度为 0,不产生脉冲信号;当 A\_Value = B\_Value 时,产生的脉冲宽度为 A\_Value(或 B\_Value)  $\times$  0.833 ns;其他取值情况下,如果时钟频率取值为 50 MHz 和 48 MHz,初值装载信号为 1 MHz,要使模块能在下一次初值重新装载前能够产生指示信号,计数值 A\_Value 和 B\_Value 的最大分别为 49 和 47,当 A\_Value 取最大值 49,B\_Value 取最大值 47 时可以生成最大脉冲宽度,宽度为 999.167 ns。

# 2 基于双通道同步复装载的瞬态脉冲 发生系统设计

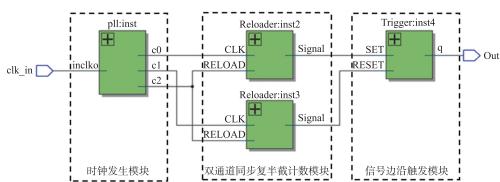

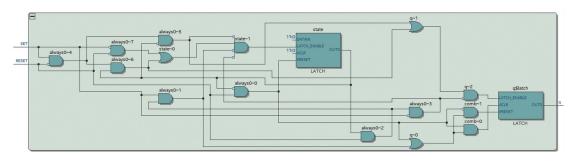

基于双通道同步复装载脉冲发生方法,本文设计了一个纳秒级瞬态脉冲发生系统,该系统的 RTL 视图如图 3 所示。

如图 3 所示,系统可以分为时钟发生模块、同步 复装载模块和信号边沿触发模块。以下本文将对这 三个重要模块设计进行详述。

图 3 系统 RTL 视图

### 2.1 时钟发生模块设计

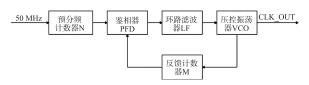

时钟作为时序电路的基础,在整个 FPGA 程序 开发过程中都十分重要。使用直接数字频率合成 (Direct Digital Synthesis, DDS)技术,可以产生任意 频率的时钟信号,多锁相环(Phase Locked Loop, PLL)也同样可以产生 FPGA 工作频率以内的任何 时钟信号组合。但是本文提出的双通道同步复装载 脉冲发生方法对产生时钟的相位同步性要求极高,上述方法均无法保证信号的初相位完全相同。为了使时钟信号的相位相等、频率稳定,双通道同步复装载脉冲发生方法的时钟发生模块使用单个锁相环进行设计。由于使用单一锁相环生成的多路时钟会受到 FPGA 内部结构制约,需要对生成的时钟频率进行精心设计。经过多次测试,生成的最佳时钟信号

组合为 48 MHz 和 50 MHz。

如图 4 所示,锁相环是一种闭环频率控制系统,本文设计的纳秒级脉冲发生器使用 Altera 的 FPGA 芯片,可以通过 IP 核对 PLL 进行参数设置。首先将外部晶振产生的 50 MHz 时钟通过预分频计数器 (N=25)产生 2 MHz 时钟送入鉴相器,鉴相器将反馈信号与输入时钟进行比较,发出控制信号经过环路滤波器驱动压控振荡器调整输出时钟频率,直到两个信号同步。当反馈回路中的反馈计数器 M=24 时,输出时钟为 48 MHz 时系统达到稳定,等效于对 50 MHz 进行了 25 分频、24 倍频输出 48 MHz 时钟信号。

由时钟发生模块产生的 50 MHz、48 MHz 时钟 将作为双通道同步复装载计数模块的工作时钟。

图 4 FPGA 芯片 PLL 结构图

### 2.2 双通道同步复装载计数模块设计

双通道同步复装载计数模块由两个复装载计数模块组成,在本瞬态脉冲发生电路设计中起核心控制作用。为了生成频率稳定的脉冲信号,两个通道模块输出的指示信号要能够按一定周期同步稳定出现,而指示信号输出受脉冲计数值直接控制,因此,两个通道计数值能否同步复装载将对生成的脉冲信号造成重大影响。

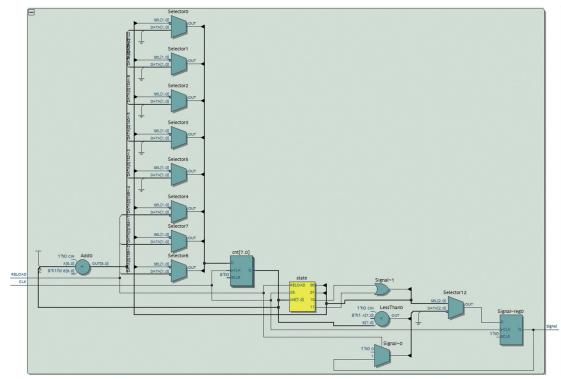

为了实现计数值的周期性同步复装载,本文给出一种复装载计数模块设计方法,其 RTL 视图如图 5 所示。

如图 5 所示,复装载计数模块以寄存器 state 进行状态机设计,状态机状态受到输入的 RELOAD 信号和计数值 cnt 共同控制。初始状态机工作状态为 0,由 Selector12 选择输出 Signal 信号为 0,八位计数 寄存器 cnt 的值每一位都受到选择器控制为一固定值保持不变,等待装载信号装载计数值。当 RELOAD 信号上升沿到来时,状态机工作状态变为 1,寄存器 cnt 被赋予初值后在 CLK 信号的上升沿进行递减计数,比较器在 cnt 计数到 0 时输出变化使得选择器 Selector12 输出 1 将指示信号 Signal 变为高电平,同时状态机工作状态变为 2。工作状态 2 保持一个 CLK 时钟周期,将指示信号拉低后进入状态 3。状态 3 在监测到 LOAD 信号的下降沿时,回到状态 0,等待下一个装载信号,避免了 cnt 寄存器在一个装载信号中被多次复装载。

本设计复装载模块的工作时序图如图 6 所示,由 LOAD 信号上升沿触发装载计数值 Value 开始计数,在 CLK 时钟信号的每个上升沿到来时,寄存器的值减 1,当寄存器中的值减 1 变为 0 时,计数完成,输出指示信号,保持一个时钟周期后,等待下一次装载。当下一次 LOAD 信号上升沿到来时,Value值被重新装载,再次开始计数,按一定周期生成稳定的指示信号。

图 5 同步复装载模块的 RTL 视图

当两个复装载计数模块的计数时钟信号初相位相同且使用同一个 LOAD 信号进行计数值的复装载时,就构成了双通道同步复装载计数模块。

双通道同步复装载模块计数产生的两个指示信号 Signal,通过信号边沿触发模块,生成对应的瞬态脉冲信号。

图 6 同步复装载模块工作时序图

## 2.3 信号边沿触发模块设计

信号边沿触发模块的作用是输出瞬态脉冲信号,根据同步复装载计数模块的预设计数值的不同,产生的指示信号相位差也不尽相同。要实现表1中任意宽度的脉冲信号,必须严格要求信号边沿触发模块实现在输入信号 SET 上升沿时刻,输出信号变

为高电平,在 RESET 的上升沿时刻输出信号变为低电平。当两通道同步复装载计数器的输出指示信号,即 SET、RESET 信号的上升沿时刻相距很近时,输出信号的高低电平就能在极短时间内完成翻转,生成极窄瞬态脉冲信号。本文给出一种可行的设计方法,RTL 视图如图 7 所示。

图 7 模块的 RTL 视图

电路实际由基本逻辑门和锁存器组成,锁存器分别锁存信号 state 和输出信号 q。 state 为状态量,表征 RESET 信号的当前状态。当 state 为 1 时,表示 RESET 信号的上升沿已经到来且 RESET 仍保持高电平;当 state 为 0 时,表示 RESET 信号为低电平。 state 只有在 RESET 信号状态变化时才产生变化,否则由锁存器进行锁存。 SET、RESET 信号初始状态均为低电平,此时 state 和输出 q 状态均为 0。只要 RESET 信号上升沿到来,输出 q 的锁存器复位引脚 ACLR 就会被使能,q 值被清零,然后 state 被置1。而当 SET 信号上升沿到来时,只要 RESET 信号不同时出现上升沿,经过逻辑运算后,q 锁存器的 PRESET 总能变为高电平输出 1。

本方案设计的信号边沿触发模块真值表如表 2 所示。

如信号边沿触发模块真值表所示,SET 信号为低电平,只有当 RESET 信号到达上升沿时,输出信号为 0,其他状态时输出保持原状态不变。在 SET 的上升沿处,只有 RESET 信号也同时为上升沿模块输出 0,其余状态全为 1。SET 信号处在高电平或下降沿状态时,只有 RESET 的信号的上升沿触发 0 输出,其他状态下输出保持不变。由真值表可得,只有输入信号 SET、RESET 的上升沿才能触发输出状态发生变化,SET 的上升沿使输出信号为 1,RESET 的上升沿使输出信号为 0,而当 SET 和 RESET 的上升沿一起到来时,输出信号状态变为 0。

表 2 信号边沿触发模块真值表

| SET   | 0  | 0        | 0  | 0            | <b>↑</b> | 1        | 1 | <b>↑</b>     | 1  | 1        | 1  | 1            | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ |

|-------|----|----------|----|--------------|----------|----------|---|--------------|----|----------|----|--------------|--------------|--------------|--------------|--------------|

| RESET | 0  | <b>↑</b> | 1  | $\downarrow$ | 0        | <b>↑</b> | 1 | $\downarrow$ | 0  | <b>↑</b> | 1  | $\downarrow$ | 0            | <b>↑</b>     | 1            | $\downarrow$ |

| q     | 保持 | 0        | 保持 | 保持           | 1        | 0        | 1 | 1            | 保持 | 0        | 保持 | 保持           | 保持           | 0            | 保持           | 保持           |

通过对以上各功能模块的设计,实现了纳秒级的脉冲发生。脉冲发生器首先由时钟发生模块产生50 MHz 与 48 MHz 的两路频率相近的时钟信号,分别作为同步复装载模块 Reloader\_A、Reloader\_B 的工作时钟。Reloader\_A、Reloader\_B 分别生成指示

信号 Signal\_A 与 Signal\_B,若计数值 A\_Value = B\_Value = 1, Reloader\_A 与 Reloader\_B 都将在一个工作周期后输出指示信号,由于工作频率不同,CLK\_A 的频率更高,所以 Signal\_A 的上升沿将先于 Signal\_B 到来,两者的时间差为 0.833 ns。

将 Signal\_A 与 Signal\_B 输入信号边沿触发模块, Signal\_A 作为 SET, Signal\_B 作为 RESET。信号边沿 触发模块只有在信号的上升沿才会触发输出变化,当 Signal\_A 的上升沿到来时,输出信号变为 1,0.833 ns 后,Signal\_B 信号的上升沿将输出信号置 0,这样就产 生了一个宽度为 0.833 ns 的窄脉冲信号。

## 3 实验结果与分析

#### 3.1 实验结果验证

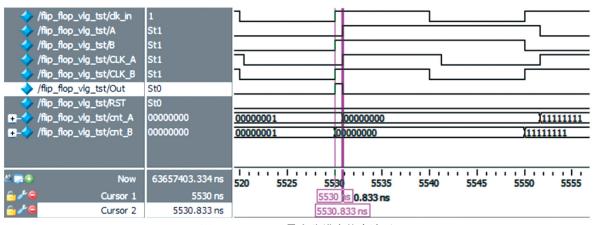

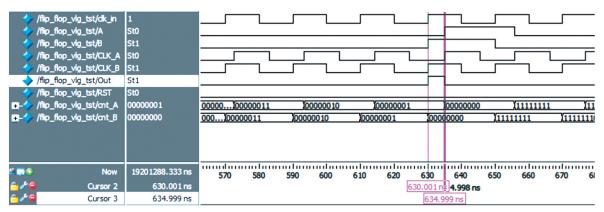

采用 Modelsim 软件进行功能性仿真。为了测

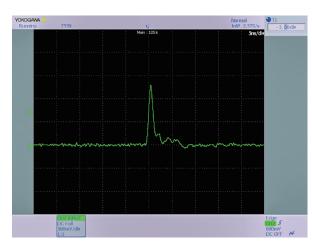

试脉冲宽度的最小精度,将同步复装载模块的计数值均设置为1,使用50 MHz 方波作为输入时钟。实验结果如图8所示。

当双通道同步复装载计数模块的初始计数值都为1时,生成的脉冲宽度应为双通道同步复装载脉冲发生方法能产生的最小脉冲宽度,也是脉冲宽度调节的最小分辨率。根据脉冲宽度计算公式,生成的脉冲宽度应为0.833 ns,与 Modelsim 仿真结果相同,最小分辨率仿真正确。

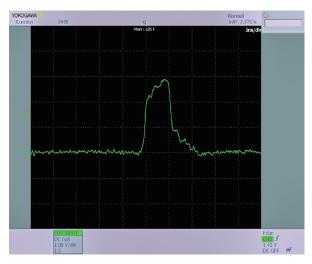

当计数值都设置为6时,仿真波形如图9所示。

图 8 Modelsim 最小分辨率仿真波形

图 9 ModelSim 功能性仿直波形

由图 9 可见,利用 Modelsim 标尺计算出的脉冲宽度值显示为 4.998 ns,而根据脉冲宽度计算公式,当初始计数值都为 6 时,输出的脉冲宽度应为 4.998 ns,结果完全一致,实验脉宽调制功能性验证结果正确。

下面使用示波器对 FPGA 实际生成的脉冲信号进行测试。FPGA 使用 Altera 的 EP4CE15F23C8 芯片。示波器型号为横河 DL9240, 其模拟带宽为1.5 GHz,最高实时采样率为10 Gsample/s。下图脉冲信号的设定值分别为0.833 ns 和4.998 ns。

图 10 与图 11 分别为设定宽度 0.833 ns 和 4.998 ns 的信号波形,每格代表的时间均为 5 ns,通过对脉冲信

图 10 0.833 ns 脉冲信号波形

号有效部分宽度测量,图中所示的实际脉冲信号与设定值吻合。示波器的结果显示该脉冲发生器实现了 纳秒级脉冲信号发生及脉冲宽度调制。

图 11 4.998 ns 脉冲信号波形

#### 3.2 实验数据分析

通过对上述实验数据的分析,双通道同步复装 载脉冲发生方法与其他窄脉冲发生方法的各项性能 如表 3 所示。

表 3 双通道同步复装载脉冲发生方法 与其他方法生成脉冲参数

|                | 参数                  |                     |            |  |  |  |  |

|----------------|---------------------|---------------------|------------|--|--|--|--|

| 方法             | 最小<br>分辨率           | 最小<br>脉宽            | 脉宽是<br>否可调 |  |  |  |  |

| 直接计数法          | 2.5 ns              | 2.5 ns              | 是          |  |  |  |  |

| 脉冲的编译码生成方法[9]  | 2 ns                | 2 ns                | 是          |  |  |  |  |

| 双三极管并联电路[11]   | _                   | 1.6 ns              | 否          |  |  |  |  |

| 双非门结构设计[12]    | _                   | $0.15  \mathrm{ns}$ | 否          |  |  |  |  |

| 双通道同步复装载脉冲发生方法 | $0.833~\mathrm{ns}$ | $0.833~\mathrm{ns}$ | 是          |  |  |  |  |

直接计数方法是利用 FPGA 内部锁相环将外部晶振频率倍频,将其作为计数时钟进行计数,生成1 ns 分辨率的脉冲信号需要至少1 GHz 稳定工作频率,通用 FPGA 显然难以达到要求。脉冲的编译码生成方法利用脉冲信号只有1和0两种状态,将脉冲信号以时间片的形式进行切割,每个时间片的脉冲状态用一位二进制数表示。通过上位机将二进制序列数据发送到 FPGA 中就可以生成对应的脉冲信号。但是编译码的最小时间片精度受到 FPGA 本身工作频率制约,难以实现更高的分辨率。

除此之外,双三级管并联电路利用 LC 电路阻 尼原理和双射频三极管并联产生的雪崩效应,产生 了幅度较大的脉冲信号,但脉冲宽度也较大。而利 用数字逻辑器件的竞争冒险实现窄脉冲发生的双非 门结构设计虽然生成了极窄脉冲信号,但是其脉冲宽度受制于电路设计,无法进行调节。

直接计数法和脉冲的编译码生成方法是通过提 高 FPGA 自身工作频率来提高最小分辨率的。通常 的 FPGA 工作频率一般都在 500 MHz 以内,脉冲宽 度调制的最小分辨率不会小于 2 ns。与其原理不 同,本文设计的双通道同步复装载脉冲发生方法在 有限的 FPGA 工作频率下,使用双通道同步复装载 计数模块分别对频率相近的 48 MHz 和 50 MHz 时 钟信号计数并产生指示信号。两个通道的指示信号 之间会因为游标效应产生相位差。利用相位差产生 窄脉冲的等效工作频率可以达到 1 GHz 以上, 而与 FPGA 本身的最大工作频率无关,因此最终能够达 到 0.833 ns 的纳秒级脉冲分辨率。不仅如此,双通 道同步复装载脉冲发生方法的 0.833 ns 最小脉冲宽 度相比脉冲宽度不可调节的双三极管并联电路设计 仍然具有显著优势。双非门结构设计可以生成最小 脉宽为 0.15 ns 的窄脉冲信号,但电路设计完成后, 脉冲宽度无法调节,很难加以应用。本文的方法不 仅实现了 0.833 ns 的窄脉冲信号的发生,也实现了 0.833 ns 的脉冲宽度调节精度。

## 4 结论

本文提了一种双通道同步复装载脉冲发生方法。由时钟发生模块产生两个频率相近的计数时钟和同步装载信号,输出给同步复装载计数模块。当同步复装载计数模块的计数值满足条件时,输出指示信号给信号边沿触发模块生成所需宽度的脉冲信号,实现了纳秒级脉冲信号的 FPGA 直接输出。实验结果表明,双通道同步复装载脉冲发生的最小脉冲宽度为0.833 ns,脉宽调节精度也为0.833 ns,和现有的FPGA 脉冲发生技术相比,达到了更窄的脉冲宽度和更高的脉宽调节精度,和无法调节脉宽的窄脉冲发生技术相比,设计更为灵活。本文的方法实现了纳秒级的瞬态脉冲信号发生和精度更高的脉冲宽度调制。

双通道同步复装载脉冲发生方法实现了纳秒级的瞬态脉冲信号发生和脉冲宽度调制,达到了预期的设计目的。在此基础上,该方法还可以生成更高分辨率的脉冲信号。但是受目前示波器的带宽限制,难以对更高分辨率的脉冲信号进行准确观测,将在今后的研究中改进设计,进一步提高脉冲信号的分辨率。

### 参考文献:

[1] 顾丽爱. 超宽带脉冲产生电路的研究与设计[J]. 现代电子技术,2016,39(3):131-134.

- [2] 李宇,路崇,叶威,等.一种基于双三极管并联的 UWB 窄脉冲 发生器[J]. 电子器件,2017,40(2):333-336.

- [3] 程昊腾. 极窄脉冲信号调理技术研究[D]. 成都:电子科技大学,2015.

- [5] 赵梓光.亳微秒脉冲的发生和显示[J]. 复旦大学学报(自然科学),1963(1):47-53.

- [6] 顾玉辉,李柯,朱明武.一种虚拟信号分析仪器的设计[J]. 电子测量与仪器学报,1999(1):51-55.

- [7] 何其锐,杨健君,廖云,等. 利用单片机和 CPLD 实现高速信号 发生器[J]. 电子器件,2006,29(1);197-200,204.

- [8] 李白燕,张健. 一种改进的数字单脉冲技术抗干扰特性研究 [J]. 电子器件,2016,39(5):1098-1102.

- [9] 田宇. 基于 FPGA 的高速可编程的脉冲信号发生器的设计 [D]. 合肥:合肥工业大学,2018.

- [10] 黎燕兵,万生鹏,胡元华,等. 基于 FPGA 的多用途信号发生器的设计[J]. 现代电子技术,2016,39(13):72-76.

- [11] 李宇,路崇,叶威,等. 一种基于双三极管并联的 UWB 窄脉冲 发生器[J]. 电子器件,2017,40(2);333-336.

- [12] 赵红梅,王园璞,崔光照.双非门结构皮秒级窄脉冲设计[J]. 电子器件,2015,38(3):548-552.

- [13] 铁维昊,赵程光,孟萃,等. 旋磁型非线性传输线调制脉冲特性数值分析[J]. 高电压技术,2019,45(1):301-309.

- [ 14 ] Wang X W, Wang L, Xiao F, et al. Generation of 88 as Isolated Attosecond Pulses with Double Optical Gating [ J ]. Chinese Physics Letters, 2020, 37(2):16-19.

- [15] Koushki A M. Generation of Single Isolated Attosecond Pulse from a Monolayer hexagonal Boron Nitride Using a Polarization Gating Technique [J]. Optics Communications, 2020;466;125679.

王薪贵(1999—),男,硕士研究生,研究方向为 FPGA 高速信号处理与电子电路设计,xingui\_wang@ 126.com;

吴 迪(1980—),男,博士,硕士生导师, 江苏省生物医学信号检测委员会委员, 研究方向为信号与信息系统、嵌入式系 统与电子设计等,wudi@suda.edu.cn。